#### **CAMBRIDGE INTERNATIONAL EXAMINATIONS**

**Cambridge International Advanced Level**

#### MARK SCHEME for the October/November 2015 series

# 9608 COMPUTER SCIENCE

9608/33

Paper 3 (Written Paper), maximum raw mark 75

This mark scheme is published as an aid to teachers and candidates, to indicate the requirements of the examination. It shows the basis on which Examiners were instructed to award marks. It does not indicate the details of the discussions that took place at an Examiners' meeting before marking began, which would have considered the acceptability of alternative answers.

Mark schemes should be read in conjunction with the question paper and the Principal Examiner Report for Teachers.

Cambridge will not enter into discussions about these mark schemes.

Cambridge is publishing the mark schemes for the October/November 2015 series for most Cambridge IGCSE<sup>®</sup>, Cambridge International A and AS Level components and some Cambridge O Level components.

| Page 2 | Mark Scheme                                             | Syllabus | Paper |

|--------|---------------------------------------------------------|----------|-------|

|        | Cambridge International A Level – October/November 2015 | 9608     | 33    |

### **1** (a) (i) 00101000 00000011

| = <u>0.0101</u> × 2 ↑3 | [1] |

|------------------------|-----|

| =10.1                  | [1] |

| =2.5                   | [1] |

(ii) For a positive number (mantissa starts with a zero) [1] bit after binary point (second bit from left) should be a one [1]

(iii) 00101000 00000011 = 01010000 00000010 [1+1]

**(b) (i)** 01111111 0111111 [1+1]

(ii) 01000000 1000000 [1+1]

(iii) number will become too large to represent [1] which will result in overflow [1]

#### (c) Any point 1 mark

0.1 cannot be represented exactly in binary

0.1 represented here by a value just less than 0.1 the loop keeps adding this approximate value to counter until all accumulated small differences become significant enough to be seen

[max 3]

[1+1]

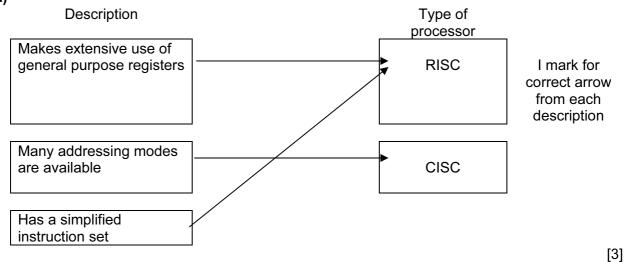

2 (a)

| Token           Symbol         Value         Type           Counter         60         variable           1.5         61         constant           Num1         62         variable |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Counter 60 variable  1.5 61 constant                                                                                                                                                 |

| 1.5 61 constant                                                                                                                                                                      |

|                                                                                                                                                                                      |

| Num1 62 veriable                                                                                                                                                                     |

| Null 1 02 Variable                                                                                                                                                                   |

| (5.0) (63 constant                                                                                                                                                                   |

(b) 6 6 6 0 6 4 6 0 6 0 0 3 2 2 2 В

www.dynamicpapers.com

Syllabus Paper

| Page 1       | <u>,                                    </u> | Mark Sahama                                                                                                                                                                      |                  |             |

|--------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|

| Page 3       | <u> </u>                                     | Mark Scheme Cambridge International A Level – October/November 2015                                                                                                              | Syllabus<br>9608 | Paper<br>33 |

| (c)          | (i)                                          | Code optimisation                                                                                                                                                                |                  | [1]         |

|              | (ii)                                         | LDD 234<br>ADD 235                                                                                                                                                               |                  | [1]         |

|              |                                              | ADD 236<br>STO 233                                                                                                                                                               |                  | [1]         |

|              |                                              | 1 mark for first 2 lines, 1 mark for last 2 lines, with no other lines ac                                                                                                        | lded             |             |

|              | (iii)                                        | Code has fewer instructions/occupies less space in memory when minimises execution time of code//code will execute faster                                                        | executed         | [1]<br>[1]  |

| 3 (a)        | •                                            | point 1 mark                                                                                                                                                                     |                  |             |

|              | rec                                          | ider's IP address<br>eiver's IP address<br>:ket sequence number                                                                                                                  |                  |             |

|              |                                              | ecksum                                                                                                                                                                           |                  | [Max 2]     |

| <b>/</b> b.\ | Λ                                            | , maint 4 magnis                                                                                                                                                                 |                  |             |

| (a)          | -                                            | y point 1 mark                                                                                                                                                                   |                  |             |

|              | pac<br>pac                                   | ail has been split up into packets<br>ket has destination address<br>kets pass through many different routers in journey<br>kets don't take same route                           |                  |             |

|              |                                              | ters use IP addresses<br>kets reassembled at destination to rebuild email                                                                                                        |                  | [Max 3]     |

| (c)          | Any                                          | point 1 mark                                                                                                                                                                     |                  |             |

|              | time<br>so                                   | ail message is only read when all of it is received e delays due to lost/delayed packets not significant sending different packets by different routes is not issue/is efficient |                  |             |

|              | •                                            | ckets arriving out of order not an issue requirement for a continuous circuit (circuit switching)                                                                                |                  | [Max 2]     |

| (d)          | Circ                                         | cuit switching                                                                                                                                                                   |                  | [1]         |

| (e)          | e.g                                          | . real-time video/video conferencing                                                                                                                                             |                  | [1]         |

| A            | ٩ny                                          | point 1 mark                                                                                                                                                                     |                  |             |

| f            | ull b                                        | it made available is dedicated to this communication stream andwidth available / no sharing est packets                                                                          |                  |             |

|              |                                              | anteed quality of service                                                                                                                                                        |                  | [Max 2]     |

| Page 4 | Mark Scheme                                             | Syllabus | Paper |

|--------|---------------------------------------------------------|----------|-------|

|        | Cambridge International A Level – October/November 2015 | 9608     | 33    |

## (b) (i)

#### Time Interval

| stage                    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |                                  |

|--------------------------|---|---|---|---|---|---|---|---|---|----------------------------------|

| Fetch instruction        | Α | В | С |   |   |   |   |   |   |                                  |

| Decode instruction       |   | Α | В | С |   |   |   |   |   |                                  |

| Execute instruction      |   |   | Α | В | С |   |   |   |   | Completing the As (1 Mark)       |

| Access operand in memory |   |   |   | Α | В | С |   |   |   | B in column 2,<br>Row 1 (1 Mark) |

| Write result to register |   |   |   |   | Α | В | С |   |   | Remainder completed (1 Mark)     |

|                          |   | 1 |   |   |   |   |   |   |   | [3]                              |

(ii) With pipelining no of cycles = 7 [1]

[1] Without pipelining no of cycles = 3 \* 5 = 15

[1] No of cycles saved = 8

| Page 5 | Mark Scheme                                             | Syllabus | Paper |

|--------|---------------------------------------------------------|----------|-------|

|        | Cambridge International A Level – October/November 2015 | 9608     | 33    |

5 (a) (i)  $\overline{A}$  .B.C +

A.B. <u>C</u> [1]

A.B.C [1]

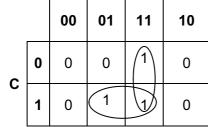

(ii)

AB

|   |   | 00 | 01 | 11 | 10 |

|---|---|----|----|----|----|

| • | 0 | 0  | 0  | 1  | 0  |

| С | 1 | 0  | 1  | 1  | 0  |

[1]

[2]

(iii)

AB

1 mark for each loop

Allow f.t. from (ii)

(iv) X = A.B

A.B + B.C [1]

Allow f.t. from (iii)

| Page 6 | Mark Scheme                                             | Syllabus | Paper |

|--------|---------------------------------------------------------|----------|-------|

|        | Cambridge International A Level – October/November 2015 | 9608     | 33    |

(b) (i)

1 mark row headings

1 mark column headings

1 mark per 2 correct rows (based on headings)

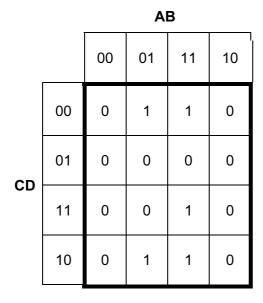

(ii)

|    |    |    | A  | В  |    |

|----|----|----|----|----|----|

|    |    | 00 | 01 | 11 | 10 |

| CD | 00 | 0  | 5  | 1) | 0  |

|    | 01 | 0  | 0  | 0  | 0  |

|    | 11 | 0  | 0  | 1  | 0  |

|    | 10 | 0  | 1  | 1  | 0  |

1 mark for loop with two 1s

1 mark for looping the four 1s

[2]

[1] [1]

[4]

(iii)

$$X = B.\overline{D} + A.B.C$$

| Page 7 | Mark Scheme                                             | Syllabus | Paper |

|--------|---------------------------------------------------------|----------|-------|

|        | Cambridge International A Level – October/November 2015 | 9608     | 33    |

6

| (a | A program is the written code ("static") A process is the executing code ("dynamic")                                                                                                                                                                         | [1]<br>[1]        |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| (b | vhen process is executing it is allocated a time slice (running state)// process is allocated time on processor when time slice completed process/interrupt occurs can no longer use processor even though it is capable of further processing (ready state) | [1]<br>[1]        |

|    | ready, running: process is capable of using processor (ready state) OS allocates processor to process so that process can execute (running state)                                                                                                            | [1]<br>[1]        |

|    | running, blocked: process is executing (running state) when it needs to perform I/O operation placed in blocked state – until I/O operation completed                                                                                                        | [1]<br>[1]        |

| (0 | when I/O operation completed for process in blocked state process put in ready state OS decides which process to allocate to processor from the ready queue                                                                                                  | [1]<br>[1]<br>[1] |

| (0 | l) high-level scheduler: decides which processes are to be loaded from backing store into memory/ready queue                                                                                                                                                 | [1]<br>[1]        |